オープンソースを活用し先進技術で迅速な IoT 組込設計 – ファームロジックスが御社のビジネスをしっかりサポートします

6月21日は夏至です。東京では日の出が4時25分、日の入りは19時だそうです。ちなみに北海道の根室では3時37分と19時02分、沖縄県の石垣島では5時56分と19時35分とのこと。日本が東西南北に広いことを実感します。

ファームロジックスは、組込機器と IoT アプリケーションのソフトウェア設計に特化し、その豊富な実績と技術力を誇ります。ソフトウェア設計だけでなく、必要に応じてハードウェアの設計や試作まで一貫して対応いたします。神奈川県相模原市に拠点を置き、地域の中小企業様へ最先端のデバイスと設計技術を提供し、コスト効率の良い迅速なソリューションを実現します。お気軽に御相談ください。(contact@flogics.com)

ファームロジックスについて

ファームロジックスは、20年以上にわたる設計と半導体技術の経験を基に、2014年に設立されました。設立以来、上場企業を含む 20社以上のお客様のニーズに応え、信頼されるソリューションをお届けして参りました。設立前には、通信機器メーカーでの携帯電話やインターネット電話交換機の設計、さらに米国系半導体メーカーでの国内大手携帯電話基地局メーカー向けハイエンド DSP 製品のサポートに携わってきたことで、幅広く豊富な実務経験がございます。

小さな技術者集団ですが、業界トップクラスのスキルを誇るパートナーと共に、世界的な視点でお客様を親身にお手伝いして参ります。

現在の主な業務領域は以下の通りです。

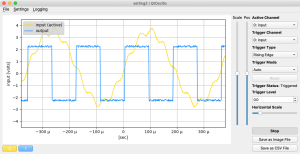

- TI C6000 DSP のソフトウェア技術(フレームワーク技術, 信号処理アプリケーション)

- Raspberry Pi や Arduino を用いたハードウェアやソフトウェアの迅速な試作

- 工場生産ラインや農業生産現場などを遠隔からリアルタイムに可視化(IoT, データ分析)

- AI(人工知能), ChatGPT 応用, コンピュータビジョンの設計

- 組込ソフトウェアの技術トレーニングから、電子工作会まで

御予算に応じた、最適な解法を提案させて頂きます(もっと詳しく)

得意分野と過去の実績

ファームロジックスは、組込設計のラピッド・プロトタイピングを得意としております。Raspberry Pi(ラズパイ)、Arduino(アルデュイーノ)を活用し、お客様のアイデアや課題に対する迅速な試作を実現します。試作においては、最新のソフトウェア技術と、高性能でコスト効率の良いマイコンデバイスを使用しております。

また、半導体メーカーにおける豊富な顧客サポート経験を元に、特に中小規模のお客様向けに、半導体メーカーや特約店に代わるサポートを行っております。お客様のニーズに応じた最適な解決策を提案いたします。

これまで、国内大手通信機器メーカーから中小企業まで、幅広いお客様に対して設計技術を提供して参りましたが、代表的な実績は以下の通りです。

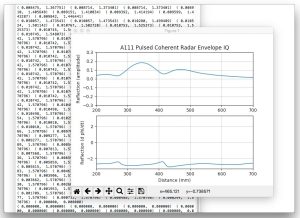

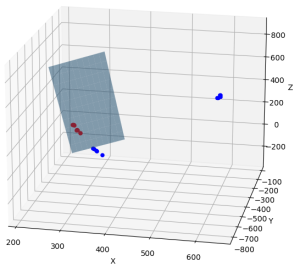

- 高齢者見守りアプリケーション:

テキサスインスツルメンツ社の C6000 シリーズ DSP を活用した、センサベースの高齢者見守りアプリケーション設計。DSP ソフトウェアのフレームワークを構築し、高速信号処理ルーチンを開発しました。

- 産業用アプリケーションへの AI 技術導入:

光学センサに基づく産業用アプリケーションへの機械学習技術の導入。サポートベクトルマシン(SVM)を用いた設計で、パラメタ決定の効率と判定の信頼性を大幅に向上させました。

- マルチチャネル 4K 動画処理システム:

FPGA を用いたマルチチャネル 4K 動画処理システムの設計支援。短納期の案件において、ソフトプロセッサコア向けファームウェア設計と FPGA システム設計の問題解決に取り組みました。

お客様を最新技術でサポート

ファームロジックスでは、お客様のニーズに合わせた最適な技術でサポートいたします。

- マイクロプロセッサの選定:

お客様の設計資産を考慮し、幅広いメーカーの製品群から最適な半導体を選定します。旧製品や特定メーカーにこだわることなく、最適な選択を提案いたします。 - 設計ツールとプログラミング言語:

近年の多様な開発ツールとプログラミング言語を駆使し、設計品質と生産性を向上させます。安価な純正デバッグプローブや無償の開発ツールにより、設計コストを最小限とします。 - 無償ソフトウェアライブラリの活用:

豊富な経験に基づき、信頼性と性能に優れたソフトウェアライブラリを提案します。多くの技術者によって広く検証されているライブラリの活用により、迅速かつ高品質な設計を可能とします。

ファームロジックスの 3つの約束

- お困りのお客様をお待たせしません

- メールで御要求を伺ってから、最速で半日以内に御見積をいたします。御社訪問を伴う打合せは通常不要です。お問い合わせから納期までの最短化に注力します。(お問合せからアフターサポートまでの流れ)

- 御社にて未受注のプロジェクトであっても、技術評価や実現性検討など、先行してお手伝いさせて頂きます。御遠慮なく御相談ください。

- 全てを御社にお見せします

- 設計に使用している部品、ソフトウェア、参考とした外部技術資料を開示いたします。

- パートナーや協力会社の優れた技術や製品には、最大限の敬意を払います。私共が作り上げたように見せかけることは致しません。

- 業界トップクラスの低コストをお約束します

- 設計工程だけでなく、お問合せから納品まで徹底して無駄を省くことで、他社が真似のできない低コストで御社の御要求に応えます。

- 仕入価格高騰、エネルギー価格高騰の中でも、働き手の生活を守りたい経営者様を応援いたします。先端の半導体デバイス、オープンなソフトウェア設計ツールなどを駆使することで、設計コストは大幅に削減可能です。一過的な初期コストの低減ではなく、トータルコストの削減をお手伝いします。

何かを決めてしまう前に、お支払いになる前に、まずは御相談ください。デバイスや開発環境の選定でプロジェクトの成否が決まる、と言っても過言でありません。(御相談は無料です)

特集: IoT ウェブアプリケーションのデモをまとめてみました

- [リアルタイム] 弊社オフィス(相模原市南区)の PM 2.5 飛散状況:説明

- [リアルタイム] PM 2.5 飛散量と過去 10日の傾向比較:説明

- [画面キャプチャ] スマートプラグ電力量の移動移動平均グラフ

- [テストデータ] オキシメーター SpO2 の遠隔常時監視:説明

電子工作とプログラミング教室の選びかた

流行りの ChatGPT を使って、お子さま向けの教室選びの相談に乗ってくれるチャットボットを作ってみました。まだ、AI に与えている知識が十分とは言えませんが、お試しください。

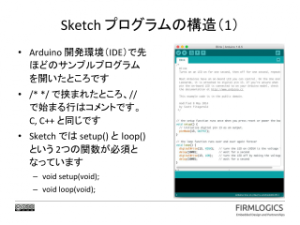

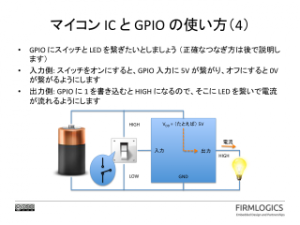

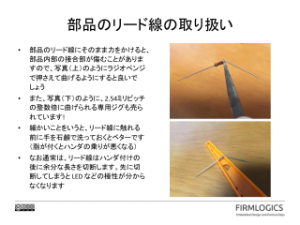

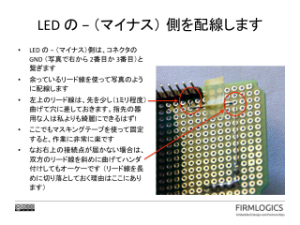

公開: 電子工作会のプレゼンテーション資料

以前、Arduino を使った電子工作会を開催しましたが、その時に作成したプレゼンテーション資料(150ページ)が眠っていましたので、公開させて頂きます。人気の Arduino(アルデュイーノ)マイコンの紹介から、工具と部品の揃えかた、電子回路の基礎、初歩のハンダ付けまで、内容は盛りだくさんです。商利用を除き、原則として御自由にお使いください。(ライセンスは CC BY-NC-SA 4.0 とします。)

プレゼンテーション資料を拡大して見たい場合は、上のリンクを辿ってください。

お問い合わせはお気軽に!

以下のフォームではなく、直接メールにてお問い合わせ頂くことも可能です。こちらを御覧ください。

![Illustration for a small tech company's website banner. The scene captures a close-up of a tidy electronics workbench in a bright room. A powerful PC setup with dual modern LCD monitors dominates the desk, one showing coding in progress and another showing a 3D plotting. Keyboard is classic and mechanical one. Only one computer mouse is located at right hand. Behind the PC is a wall with framed technical charts. There is also a shelf on the wall, containing two or three tasteful decorations favored by engineers. Essential gadgets, including an eye-catching, brand-new digital oscilloscope with large screen and a well-worn power source, sit neatly above the screens. The desk's right has a green protective sheet, a large and complicated electronic board wired to the aforementioned gadgets, a screw driver, a pair of tweezers, and hints of soldering tools. A touch of greenery peeks from a window beside the workbench, contrasting the high-tech environment. The whole image has a soft and warm hue, but gives a sense of hope for the future to audiences. Illustrated by Black Forest Labs FLUX.1 [pro].](http://flogics.com/wp/wp-content/uploads/2024/08/flogics15_guidance3_interval4_retouch2.jpg)