PolarFire SoC Icicle Kit が動いたら次はどうする?

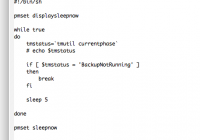

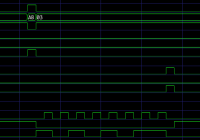

Running pre-installed demo of PolarFire SoC Icicle Kit. さて。昨日はブログ記事を書くだけで終わってしまったので、今日はさっそく、PolarFire SoC Icicle Kit の「火入れ」をしてみたいと思います。ちなみに「ボードの火入れ」って英語でなんて言うんだろう。burn-in だと、ちょっと意味が違いますよね。 さらに末尾に、Linux 環境のアップデート、ビットストリームの生成、Linux のリビルド、FPGA… 続きを読む »