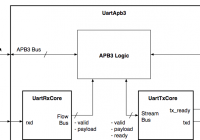

[SpinalHDL] 本家 UART コードを読み解く

Reading SpinalHDL original UART code to get better insight. いままで、SpinalHDL で自前の UART を書いてきましたが、今日は SpinalHDL 本家の UART コードを読んでみました。どうも私は人様の書いたコードを読むのがあまり好きでないようで、ちょっとモチベーションが湧かなかったのですが、優秀な先達技術者の設計を読むのは大事ですし(「チャンスがあればいつでもコードを盗め」でしたっけ?)、いまならまだ… 続きを読む »