ソフト屋のための SpinalHDL FPGA 設計入門(その3)

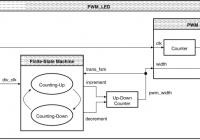

Continue sleepy LED PWM project by SpinalHDL. 前回の続きです。前回までで PWM の基本ロジックが完成したので、今回は LED ホワホワルーチン、じゃなかった、ホワホワロジックを設計していきましょう。 前回までの流れ 初めての SpinalHDL: デジタル PWM を SpinalHDL で書いてみよう Verilog 生成とシミュレーション: 記述した回路をシミュレーションしてみよう 前々回に設計したブロック図を再掲します。 … 続きを読む »