投稿者「yokoyama」のアーカイブ

RISC-V ソフトコア VexRiscv の始め方(その1)

How an FPGA beginner (or me) start evaluation of VexRiscv. 前々回の宿題で、nextpnr を動かした後は picorv32 の詳細を勉強しようと思ってましたが、ちょっと方針を変更して、VexRiscv をいじってみようと思います。その理由としては、 VexRiscv ではキャッシュコントローラが提供されていること(RAM をあまり持たない FPGA、SPI フラッシュメモリを持っている TinyFPGA BX では、… 続きを読む »

TinyFPGA BX で RISC-V を動かしてみる(nextpnr 編)

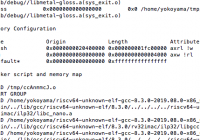

Now using nextpnr instead of Arachne-pnr. さて、一つ目の宿題をやってみます。前回は placing and routing に Arachne-pnr を使いましたが、今回は nextpnr を試してみます。 nextpnr は、こちらからダウンロードしてインストールしました。バージョンはコミット dd7f7a5 です。 Makefile を書き換える まず、TinyFPGA-BX/examples/picosoc のオリジナル Ma… 続きを読む »

TinyFPGA BX で RISC-V を動かしてみる(その1)

Running RISC-V (picorv32) on TinyFPGA BX. Yosys、arachne-pnr の動かし方の基本を理解し、RISC-V のアーキテクチャも少し分かってきたので、当初の目標「FPGA で RISC-V を動かす」にチャレンジしてみようと思います。実はチャレンジも何も、ネットでたくさんの事例が紹介されているのです。ただし、私は FPGA についてはほとんど素人ですので、基本を理解する良いテーマだと思いました。 RISC-V の HDL 実装… 続きを読む »

[小ネタ] Mac OS の Time Machine を一時的に停止する

Temporarily disabling Mac OS Time Machine. 今日は小ネタです。(ここ数日、いろいろ長い記事を書きまくったので。) Mac OS を使っている方は、Time Machine という機能を御存知かと思います。 定期的に、ディスクのバックアップをしてくれるツールですね。 もしかすると最近のバージョンの Mac OS ではいろいろ改善されているのかも知れませんが、Time Machine は、いろいろと痒いところに手が届かないツールでもありま… 続きを読む »

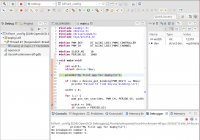

Zephyr でビルドした RISC-V コードを Eclipse でデバッグする

Debugging HiFive1 program built with Zephyr OS, on Eclipse IDE. 昨日は Zephyr OS 環境を使って SiFive HiFive1 のソフトを書く練習をしてみました。今日は、ビルドしたコードを Eclipse 上の GDB でデバッグしてみましょう。 こちらでいろいろ調べてみると、ARM ターゲットのデバッグはうまく Zephyr(zephyr-sdk-0.10.3)でサポートされているようなのですが、どうも… 続きを読む »

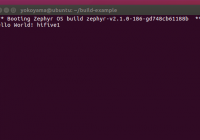

HiFive 1 のプログラムを Zephyr でビルドしてみる

Building SiFive HiFive 1 app by Zephyr OS environment. さて。昨日の続きです。 当初は SiFive の Freedom Studio を動かしてみようと思ったのですが、調べてみると、RISC-V のためのソフトウェア開発環境がいくつか登場してきていることが分かりました。GNU の toolchain があればそれでいいんじゃないの? というのは甘い考えで、組込系(に限りませんが)のプログラムをビルドするには、標準ライブ… 続きを読む »

SiFive Freedom E SDK の重箱を少しつついてみる

Slightly digging into SiFive Freedom E SDK. 今日は SiFive の Freedom Studio を試してみようと思ったのですが、もう少し SiFive Freedom E SDK の動きを調べてからにしようと思います。少し重箱つつきな感じです。 make software 編 まず最初に、make コマンドで make software するときの動作を少し追ってみます。つまり、コンパイル & リンクですね。あ、最後のほ… 続きを読む »

RISC-V ボード(HiFive 1)を動かしてみる

My first evaluation of SiFive HiFive 1 (Arduino form factor RISC-V board). 今日は、随分と以前に購入した HiFive 1 を引っ張り出してきました。これは、SiFive という会社から 2016年の終わり頃にリリースされた、RISC-V ボードなのです。基板の形は Arduino Uno などと同一であり、いくつかの Arduino シールドが流用できるようです。このボード、私は去年の 5月頃に入手し… 続きを読む »

ファームロジックスは IPv6 に対応しました

Now our website is compatible with IPv6 network technology. 本日、ファームロジックスのウェブサイト(サブドメインを除く)は、遅ればせながら IPv6 に対応しました。 Wikimedia user Matma Rex さんより(CC BY 3.0) 既に IPv6 環境をお持ちの方は御存知のように、海外のウェブサイトの多くは既に IPv6 で運用されています。 後記(2019/12/23) サブドメインも IPv6 … 続きを読む »