Received a PolarFire SoC Icicle Kit today.

かねてからリリースを待ちわびていた、Microsemi(現 Microchip)の PolarFire SoC Icicle Kit が届きました。元々は 9月中旬の出荷を目指していたようですが、FPGA のフラッシュプログラマの問題が見つかり、一月弱ほど予定がスリップしたようです。

TL; DR

PolarFire SoC Icicle Kit の詳細については後述しますが、これに興味を持った理由を簡単に説明します。

いままでファームロジックスでは、極めて高い演算能力を必要とする信号処理や制御などのリアルタイムアプリケーション向けに、Texas Instruments(以下 TI)社の C6000 系ハイエンドマルチコア DSP をメインにサポートして参りました。しかしここ数年、同社の DSP に対する投資やサポートがやや手薄になっているように感じており、そのようなアプリケーションを設計するお客様の選択肢が狭まっていることを憂慮していました。

PolarFire SoC 搭載の RISC-V コアは、クロック速度は C6000 に及ばず、また、整数および浮動小数の並列演算処理に関してもまだ十分とは言えないように思いますが、対消費電力の演算性能が優れているようであることに加えて、マルチコア(hart)を AMP(非対称マルチプロセシング)に配置することで、 Linux と RTOS を同時に動作させることができるのが特徴です。これにより、TI の KeyStone 2 SoC と同等か、あるいはより使いやすいアプリケーションプロセッサとして、お客様に提案できる可能性を秘めていると感じました。

また、近年の DSP SoC(KeyStone など)や MCU(マイコン)は、搭載のペリフェラルやアクセラレータが豊富ですが、そのいくつかは極めて限定された顧客(あるいは driving customer)向けに設計されており、他の顧客にはあまり役に立たない場合も多いと思います。そのような特殊なアクセラレータよりも、FPGA が搭載されていたほうが嬉しいお客様もあるのではないでしょうか。

最近はオープンソースの HDL 設計ツールが登場するなど、FPGA 設計の裾野も広がりつつあり、FPGA ファブリックと高速な SerDes I/O を搭載した PolarFire SoC は、お客様の厳しい御要求にも対応できるのではないかと考えています。(TL; DR 終わり)

PolarFire SoC Icicle Kit ってなに?

以前より Microsemi(現 Microchip。以下略)の FPGA で PolarFire シリーズという製品がありました。同社はまた RISC-V の展開に積極的で、以前から MI-V と呼ばれるソフトコア IP を提供していたのですが、去年、この PolarFire FPGA に、ハードコア(?)の 5コア(hart)64ビット RISC-V を追加した PolarFire SoC というデバイスを発表しました。

搭載されている RISC-V IP は有名な SiFive 社の設計のようで、

- RV64GC のアプリケーションコア(U54) × 4

- RV64IMAC のモニタ用コア(E51) × 1

という構成になっています。このような贅沢な構成なので、当然 Linux も動作します。ちなみに、コアクロックは最大 625MHz のようです。

ところで、実際に送られてくるボードではヒートシンクとクーリングファンが付いてくると思っていたのですが、ヒートシンク無しです。以前より TI 社の KeyStone などを触ってきて、数百 MHz 超のマルチコアプロセッサではヒートシンク、さらにはクーリングファンが必須と思ってきたので、これは意外です。今度、発熱を確認してみたいと思います。

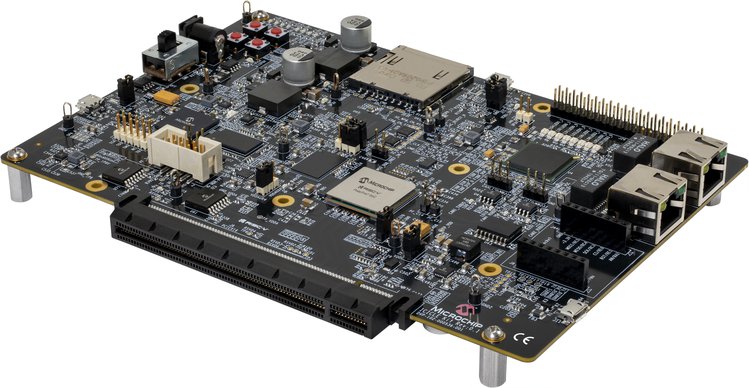

この PolarFire SoC(MPFS250T-FCVG484EES)を搭載した評価ボードが、PolarFire SoC Icicle Kit です。7月頃、Crowd Supply で発表されたので、御覧になった方もあるのではないかと思います。余談ですが、デバイスの型番や評価ボードの型番(MPFS-ICICLE-KIT-ES)を見ても分かるように、これらは ES(Engineering Sample)品であり、一般にメーカーの品質保証対象外なので、注意しましょう。

PCI Express のコネクタ(× 16)や Gigabit Ethernet を 2つ搭載した豪華な仕様ですが、ディスプレイ接続用の HDMI や、カメラ接続用の MIPI CSI-2 コネクタなどはなく、流行の AI や画像処理は、ターゲットから外しているようです。(ちなみに、FPGA デバイスのドキュメントを見ると 2× PCIe Gen 2 (×1, ×2, ×4) とありますので、× 16 のサポートはなさそうです。)

もちろん、PCIe コネクタがあるので外部に HDMI や CSI を付けることは可能でしょうが、折角の PCIe は別の用途に使いたいところで、早速このようなドーターカードが発表されています。(ただし現在は発売はされていないようで、自分でボードを起こす必要があります。また、これはハードウェアだけなので、実際に利用するには FPGA で HDMI TX を組み込み、ドライバソフトなどを書く必要がありそうです。)

ちなみに、HDMI TX などの IP については、こちらの FPGA Intellectual Property Cores に一覧があります。

評価ボードの構成

評価ボードに搭載されているデバイスは、MPFS250T-FCVG484EES というものです。比較的大きな規模の FPGA で、

- ロジックエレメント(4LUT + DFF): 254k エレメント

- 演算ブロック(18 × 18 MACC): 784 ブロック

- ブロックメモリ: 16Mビット程度

- SerDes(最大 12.5 Gbps): 4トランシーバ

- GPIO: 84ピン

というものです。以前私が遊んでいた TinyFPGA BX は 8k ロジックセル程度(こちらも 4LUT + DFF)でしたし、競合の Xilinx Zynq でいうと、Z-7030 よりは上、7035 より少し小規模、というところでしょうか。しかし一番の特徴は、搭載している RISC-V の消費電力あたりの性能が高いことではないかと思います。以下のグラフが、Microsemi 社の自信を示しています。(オレンジが PolarFire SoC MPFS095T。)

評価ボードの詳細な構成については、こちらの Microsemi: UG0882 User Guide PolarFire SoC FPGA ICICLE Kit(PDF) が参考になりますので省略します。

なお、回路図や BOM などはこちらにあります。

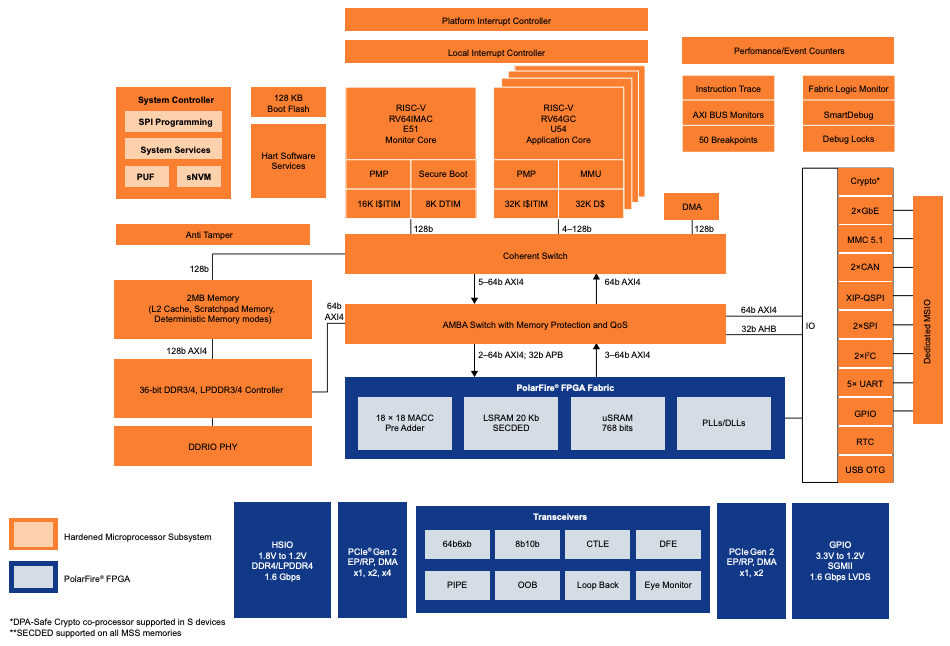

FPGA SoC の構成

デバイスの構成は次のようになっています。(PolarFire SoC Brochure より引用)

(字が潰れて読みづらいでしょうから、オリジナルの Brochure を見てください。)

オレンジ色で描かれているのが、Microsemi 言うところの MSS(Microprocessor Sub-System)に属するブロックで、青色で描かれているのが FPGA ファブリックとインターフェイス部です。

設計ツール

PolarFire SoC には、FPGA とマイクロプロセッサの両面があるので、ツールも大きく分けて 2種類があります。

- Libero SoC: FPGA 設計ツール(競合の Xilinx で言うと、ISE あるいは Vivado に相当)

- SoftConsole: Eclipse ベースのソフトウェア統合開発環境

後で簡単に説明しますが、FPGA はビットストリームという構成データをフラッシュメモリから読み取らないと動作できないので、最低限のビットストリームを用意しないと RISC-V を動作させることはできません。

ところで FPGA 設計ツールにありがちなのですが、同社の Libero SoC はライセンス管理に(悪名高き?)FLEXlm を利用しており、インストールに苦労すること請け合いです。

Libero SoC では、全てのサブモジュールを自社で設計しておらず、論理合成ツールは Synopsys 製、シミュレータは Mentor 社製です。私の場合、Libero SoC のライセンス設定はうまく行ったのですが、論理合成ツール Synplify がライセンスをうまく取得できず、苦労しました。Libero SoC に同梱のライセンスマネージャに snpslmd が含まれておらず、別途ダウンロードする必要があるのです。PolarFire SoC のために Libero SoC は大きなアップデートをしたようですが、そのためにリリースパッケージの整備が、まだ十分に追いついていない印象です。(インストールのためのドキュメントは比較的しっかり書かれているので、よく読めば大丈夫でしょう。)

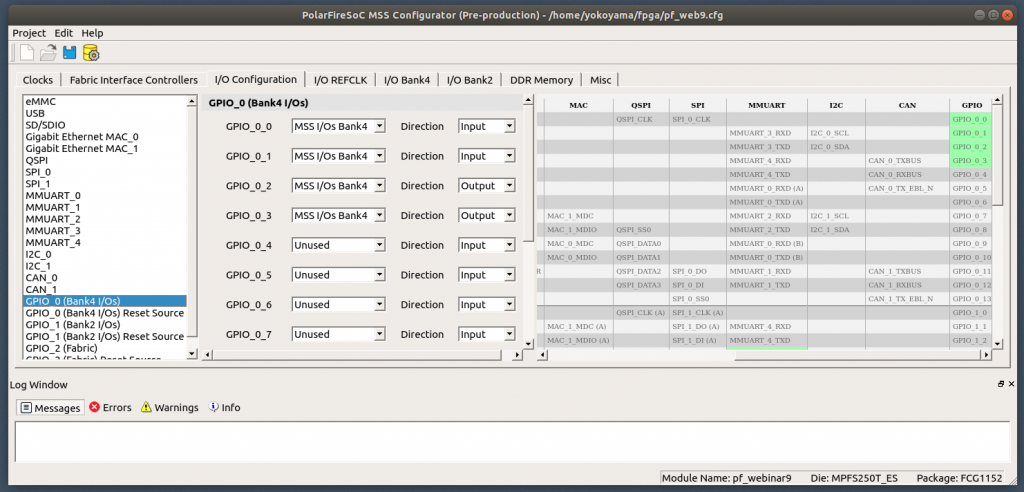

MSS コンフィグレータ

FPGA のソフトコアの構成(configuration)については、従来の Microsemi MI-V でも Xilinx の MicroBlaze でも、FPGA 設計ツールの内部で実行するもののようですが、ハードコアである PolarFire SoC の MSS では、専用のツール PolarFire SoC MSS Configurator に分離されました。ドキュメントによると、MSS のコンフィグレーションは RISC-V ファームウェア設計者が実行することもあろうから、ライセンスマネージャが必要な Libero SoC に組み込まれていると使い勝手が悪いため、というのが理由のようです。

ただし、以前のコンフィグレータに比べると、構成時に画面で IP の信号(ピン)入出力を確認できないなど、ちょっと荒削りな気がします。確かに、ファームウェア設計者は IP の信号入出力には興味ないのかも知れませんが。

以下に、PolarFire SoC MSS Configurator で GPIO のピン割当をしている画面例を示します。MSS にはマルチプレクサが内蔵されているようで、自分の使いたい機能を I/O バンクに割り当てることができます。この辺は、例えば STMicroelectronics 社の STM32CubeMX を御存知の方にはイメージしやすいのではないでしょうか。

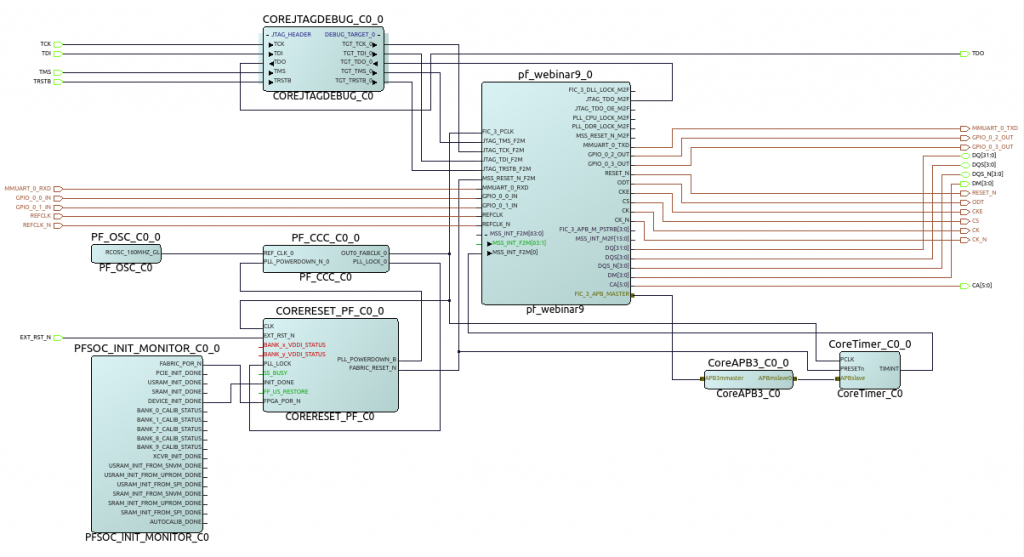

Libero SoC による周辺ファブリックの設計

前述のように、SoC 上の MSS はそのままでは動作できず、最低限の FPGA ファブリックによるブロック設計が必要です。ここでは詳細は略しますが、こんな感じのブロック構成になるようです。

なにぶん、まだテストできていないので詳細は説明できませんが、MSS 以外に以下のような IP が配置されています。

- PolarFire SoC Initialization Monitor

- CoreReset PF

- PolarFire RC Oscillators

- Clock Conditioning Circuitry

- CoreJTAGDebug

それ以外に、IP タイマを割込ソースとして利用するために、以下が配置されています。

- CoreAPB3

- CoreTimer

ファーム設計者さんから見ると「面倒くさいなあ」というところでしょうが、自分の好きなように回路ブロックを配置できるというのは面白いところです。(ま、だから FPGA なのですが…)

MSS ブートの仕組

PolarFire SoC の RISC-V MSS のブート手順については、ドキュメント Microsemi: UG0881 User Guide PolarFire SoC FPGA Booting And Configuration が詳しいですが、以下に簡単に説明します。

PolarFire SoC がリセットされると、まず最初に FPGA の Design Initialization が実行されます。これはおそらく、FPGA のビットストリームの読み込みと FPGA ファブリックの初期化処理だと思われます。

続いて、MSS Pre-Boot という処理に移り、eNVM と呼ばれるオンチップ不揮発メモリをセットアップし、MSS L2 キャッシュの冗長回路リペア処理を実行します。

最後に、MSS User Boot 処理に移ります。このブートでは、次の 4種類のブートモードの中から一つを選んで動作します。

- Idle boot(詳細不明)

- Non-secure boot(現状は、主にこれが利用される模様)

- User secure boot(現在はサポートされていない模様)

- Factory secure boot(詳細不明)

どのブートモードが使用されるかは U_MSS_BOOTMODE[1:0] という 2ビットの構成情報で決まるようですが、私の調べた限りでは、これは、SoftConsole に付属するファームウェア書込ツールで設定できるようです。(詳しくは、Microsemi: PolarFire SoC Software Development and Tool Flow User Guide(PDF)の 3.3.1 節 Programming the eNVM に記述されています。)

User Boot のブートイメージは、上述の eNVM と呼ばれる 128K バイトのメモリに格納されます。

ここから先の処理は、同社の過去のウェビナー資料では明確に説明されていませんでしたが、最近の情報によると、このブートイメージとしては通常、HSS(Hart Software Services)というファームウェアを書き込んでおき、これをモニタコア E51 で実行することになるようです。E51 上の HSS は、4つの U54 コアにプログラムをロードし、それらを起動する、という順序になるようです。HSS は GitHub のこちらに置かれていますが、詳細な説明はまだ見つかりません。ソースコードを読むしかなさそうです。(10月12日現在)

ちなみに Linux をブートする場合には、HSS から、eMMC、SD カードあるいは USB メモリなどから U-Boot を読み込み、U-Boot に制御を移した後、Linux カーネルを起動する、という手順になるようです。この辺も以下に断片的な説明がありますが、まだドキュメントが十分とは言えないように感じます。

- GitHub: Microchip PolarFire SoC Yocto BSP

- GitHub: Microchip PolarFire SoC Linux Software Development Kit

後記: HSS からU-Boot を経て Linux が起動するまでのブートの仕組は、16日の記事で詳しく説明しています。

なお、前述のようにこのデバイスはまだ ES 品です。ES の段階でこれだけの資料が公開されているというのは驚くべきことであり、Microsemi 社の気合いが窺えるというものです。資料が足りないと文句を言うのは筋違いでしょう。← 言ってるし

もう一点。上述のように、Linux のカーネルやルートイメージの生成には Yocto と Buildroot の 2種類が用意されており、後述のウェビナーを見たところでは、どちらを使うかはあなたの自由、となってました。Microsemi 社内に 2つのセクト(Yocto 派、Buildroot 派)があるように想像され、面白いところです。

ウェビナー

この PolarFire SoC の面白いところの一つは、まだ ES 品すら入手困難な段階で、月 1回のウェビナーが開催されているところです。

ちなみに私は、前者をほぼ内容確認しました。後者にはリアルタイムで参加しようと思ったのですが、なぜかウェビナーのサイトに接続できませんでした。(なんとなく、Microsemi 社のウェブサーバー、DNS あたりが最近不安定な気がします。)

その他

プログラマ FlashPRO5 が付いてきた!

今回意外だったことのもう一つに、プログラマ FlashPRO5 が付属してきたことです。なぜ意外かというと、オンボードにもプログラマが載っている「はず」だからです。それも、同社の SmartFusion2 SoC による実装、という素晴らしいもの。(意味不明)

また、ドキュメント UG0882 User Guide PolarFire SoC FPGA ICICLE Kit にも、FlashPRO5 が付属するとは書かれていません。想像するに、オンボードプログラマの問題解決が遅れたため、一緒に FlashPRO5 が同梱されたのではないかと思います。なにしろ、FlashPRO5 だけで 5〜6,000円する製品なのですから。(得をしてしまった!)

まとめ

なにぶんまだ情報が十分とは言えない状況ですが、御興味をお持ちの方がありましたら、一緒に勉強しましょう。

お問い合わせはお気軽に!

今日はここまで。