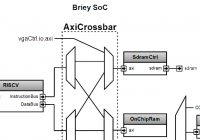

PolarFire SoC Icicle Kit ファーストインプレッション

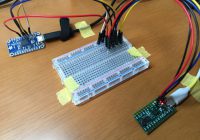

Received a PolarFire SoC Icicle Kit today. かねてからリリースを待ちわびていた、Microsemi(現 Microchip)の PolarFire SoC Icicle Kit が届きました。元々は 9月中旬の出荷を目指していたようですが、FPGA のフラッシュプログラマの問題が見つかり、一月弱ほど予定がスリップしたようです。 TL; DR PolarFire SoC Icicle Kit の詳細については後述しますが、これに興味… 続きを読む »