[PolarFire SoC] Buildroot を試してみる

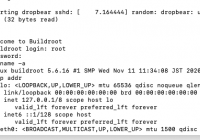

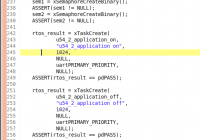

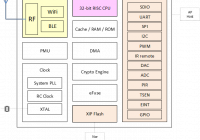

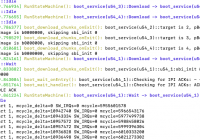

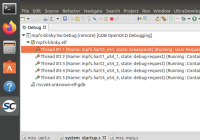

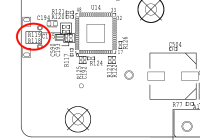

Trying Buildroot for PolarFire SoC Icicle Kit. 以前に、PolarFire SoC Icicle Kit の出荷時デモとして Yocto/OpenEmbedded の Linux を動かしてみました。今回は、代わりに Buildroot を試してみたいと思います。ビルド済イメージはないので、自分でビルドする必要があります。 なぜ Buildroot? しかし、どうして Yocto/OpenEmbedded でなく Buildroo… 続きを読む »