LiteX と Migen の勉強をしてみる(第1回)

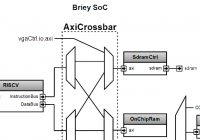

Slowly start learning LiteX and Migen. 以前に、SpinalHDL というハードウェア記述言語や、オープンソース(あまり好きな言葉ではないが)の論理合成ツール Yosys、Place and Route ツール nextpnr を使って、設計した論理回路や RISC-V SoC を Lattice 社の FPGA 上で動かしてました。 SpinalHDL による SoC 設計は面白いのですが、SpinalHDL プロジェクトの進み方は基本… 続きを読む »