「RISC-V」カテゴリーアーカイブ

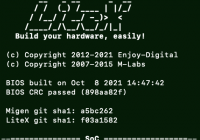

LiteX と Migen の勉強をしてみる(第1回)

Slowly start learning LiteX and Migen. 以前に、SpinalHDL というハードウェア記述言語や、オープンソース(あまり好きな言葉ではないが)の論理合成ツール Yosys、Place and Route ツール nextpnr を使って、設計した論理回路や RISC-V SoC を Lattice 社の FPGA 上で動かしてました。 SpinalHDL による SoC 設計は面白いのですが、SpinalHDL プロジェクトの進み方は基本… 続きを読む »

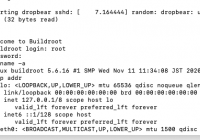

[PolarFire SoC] Buildroot を試してみる

Trying Buildroot for PolarFire SoC Icicle Kit. 以前に、PolarFire SoC Icicle Kit の出荷時デモとして Yocto/OpenEmbedded の Linux を動かしてみました。今回は、代わりに Buildroot を試してみたいと思います。ビルド済イメージはないので、自分でビルドする必要があります。 なぜ Buildroot? しかし、どうして Yocto/OpenEmbedded でなく Buildroo… 続きを読む »

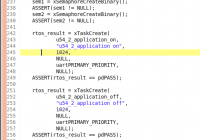

[PolarFire SoC] FreeRTOS を動かしてみる

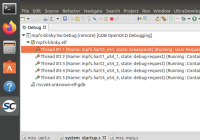

Running FreeRTOS scheduler on a PolarFire SoC RISC-V hart (core). 前回までに、PolarFire SoC の RISC-V コアで、ベアメタルライブラリを使った割込プログラミングの基本を確認しました。これにより、PolarFire SoC による製品設計の進め方が見えてきましたが、実際の設計では、やはりリアルタイム OS(RTOS)が動かないと不安が残ります。 FreeRTOS の使用例を探す GitHub: … 続きを読む »

[PolarFire SoC] RISC-V と SoC MSS の割込を理解する

Understanding interrupts of RISC-V and PolarFire SoC MSS. 23日の記事で、PolarFire SoC の RISC-V 組込プログラムを SD カードからブートするところまで確認できました。いままで、mpfs-blinky という、SoftConsole 6.4 に付属のサンプルプログラムを評価してきましたが、その名に反して、LED 点滅の機能確認を放置してきました。その理由は、同プログラムの LED 点滅には、GPI… 続きを読む »

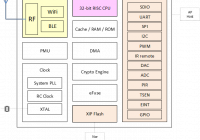

ESP32 のライバル登場か?

In a recent news, found a possible competitor for the famous ESP32, which has a RISC-V core on chip. Espressif ESP32 と言えば、組込系エンジニア、IoT エンジニアで知らない人はないほど有名な Wi-Fi マイコンです。同社は 2014年頃に一部の技術者の間で、一世代前の ESP8266 マイコンを載せた小さくて安価な ESP-01 ボードによって名前を知られる… 続きを読む »

[PolarFire SoC] 組込プログラムを SD カードからブートする

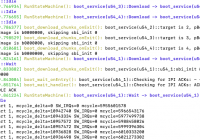

Booting an embedded program in SD card via HSS (Hart Software Services), on PolarFire SoC. 前回までに、SoftConsole 6.4 に含まれるサンプルプロジェクト mpfs-blinky を JTAG エミュレータ(FlashPro)からロードして実行することができるようになりました。プログラムの構造や、ベアメタルライブラリの使い方を勉強したい気持ちもありますが、まずは、この mpf… 続きを読む »

PolarFire SoC Icicle Kit で組込プログラミング(その2)

Updating SoftConsole sample project with the latest Bare Metal Library from GitHub, and also reflected Libero generated XML file (FPGA configuration). 前回、SoftConsole v6.4 に含まれるサンプルプロジェクト mpfs-blinky をビルドの上、Icicle Kit 上の PolarFire SoC にロードして… 続きを読む »

PolarFire SoC Icicle Kit で組込プログラミング(その1)

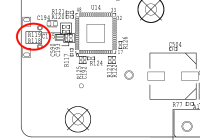

Embedded programming for PolarFire SoC Icicle kit (part 1). さて。Linux の起動も確認できましたし、ブートの仕組、メモリの使い方も少しずつ分かってきましたので、そろそろ組込プログラミングを始めましょう。 Linux がブートしないようにする 組込プログラミングの評価時には、できたら Linux はブートしないで欲しいですよね。これを簡単にできる方法はないでしょうか。一つ考えられるのは、SoC のブートモードを 0… 続きを読む »

PolarFire SoC ブートの仕組とメモリ構成

Boot procedure and memory structure of PolarFire SoC 先日は、PolarFire SoC Icicle Kit の電源を入れ、Linux のブートを確認しました。多くの皆様は既にそこまでお試しのことと思いますが、ここから先に進むにあたり、どこで何を調べたらいいのか呆然となさっている方もあるかと思います。 SoC デバイス自体に組み込まれているブートの仕組(MSS boot)については先日簡単に説明しましたが、今回は、そこから… 続きを読む »