Embedded programming for PolarFire SoC Icicle kit (part 1).

さて。Linux の起動も確認できましたし、ブートの仕組、メモリの使い方も少しずつ分かってきましたので、そろそろ組込プログラミングを始めましょう。

Linux がブートしないようにする

組込プログラミングの評価時には、できたら Linux はブートしないで欲しいですよね。これを簡単にできる方法はないでしょうか。一つ考えられるのは、SoC のブートモードを 0 に設定して、E51 コアが eNVM を読みにいかないようにすれば良いのでしょうが、(現状では)ブートモードを元の 1(non-secure boot)に戻すには ELF ファイルを与えなくてはならず、そのために毎回、HSS の ELF ファイルを指定するのは面倒です。eNVM の wearing があるかも知れないので、書換えの回数はできるだけ少なくしたいという事情もあります。

思いついた方法は、FPGA のコンフィグレーションを変更し、eMMC ではなく SD カードからブートするようにしたらどうか、というものです。そうすれば、Linux をブートしたいときは SD カードを挿入し、そうでないときは SD カードを抜いておけば良いのです。今度はそうすると、SD カードコネクタの機械的挿抜の繰り返しを心配する方もあるでしょうが、その場合は、SD カードのパーティション2(HSS ブートイメージ)の先頭セクタだけでもクリアしておけば良いでしょう。SD カードは wearing したら買い換えれば良いだけです。

SoftConsole で mpfs-blinky を動かしてみる

今回は、SoftConsole 6.4 に付属するサンプルプロジェクト mpfs-blinky を動かしてみることにしましょう。Microsemi が先月までやっていたウェビナーでは、実際にハードウェアを使ったデモはなかったので、私も何から手を付けて良いか分かりませんが、まずはプロジェクトをビルドしてみましょう。今回は L2-LIM にロードしたいので、リンカファイルとして(デフォルトの)mpfs-lim.ld を使うことにします。

プログラムをロードするには、FlashPro を繋いだ状態で、SoftConsole の Debug Configuration メニューから mpfs-blinky hw Debug.launch を選んで起動します。すると、特に何も苦労なく Eclipse のデバッグ画面に入れるので拍子抜けしました。(こちらに書いたように、VMware 上ではトラブルが起きるようですので、できたら実環境の Linux 上で試してください。)

早速、USB-UART ブリッジに仮想 COM ターミナルを繋いで(ビットレート 115.2kbps)、コアを Resume させてみました。すると、画面上にバケバケの文字が表示され続けます。。。んー。

とりあえず何か出力しようとしている様子なので、回路図を見て UART の信号をオシロで当たってみることにします。最初、CP2108 の UART1_TX_TOGG を当たってみたのですが、何も見えません。念のため、UARTn_[TR]X_TOGG を全部覗いてみましたがダメです。これらは基板上にテストパッドが出ているので、こいつかなぁ、と思ったのですが、違うようです。(悲)

回路図と CP2108 のデータシートをようく見直すと、これらのピンは通常 GPIO で、設定次第で LED 点滅に使うためのピンのようです。(再度、悲)

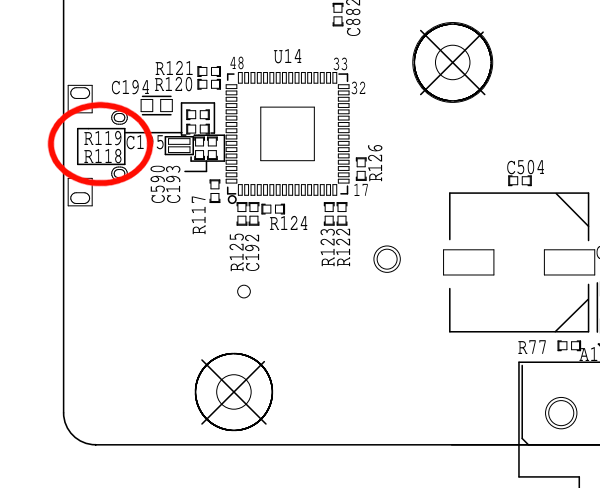

さらに回路図とレイアウト図を見比べたところ、SoC からの UART の出力は、CP2108_n_TXD(n = 1, 2, 3, 4)であることが分かりました。んー、小さなチップ抵抗にオシロプローブを当てるはめに。。。基盤裏のレイアウトを示します。R119 が CP2108_1_TXD です。

オシロを当てたところ、ビットあたりの時間が 4.4μs 程度であるので、これは 115.2kbps でなく、その 2倍の 230.4kbps であることが分かりました。ターミナルソフトのビットレートの指定を変えたら、無事に出力が見えるようになりました。

Setting outputs 0, 1 and 2 to high Setting outputs 0, 1 and 2 to low Setting outputs 0, 1 and 2 to high Setting outputs 0, 1 and 2 to low Setting outputs 0, 1 and 2 to high Setting outputs 0, 1 and 2 to low Setting outputs 0, 1 and 2 to high Setting outputs 0, 1 and 2 to low Hart 1, mcycle_delta=5264314 SW_IRQs=0 mcycle=21804859932

なぜビットレートが 115.2k ではなく 2倍の 230.4kbps になっているかを考えると、おそらく FPGA のコンフィグレーションと、bare-metal ライブラリの定義が食い違っているのだと思います。

明日以降は、その辺を調べてみたいと思います。

今日はここまで。