Critical review of OpenAI’s GPT-4V for its capabilities in understanding circuit diagrams, highlighting its limitations and room for improvement.

相模原市で IoT 設計を受託しているファームロジックスです。

先日は OpenAI 社の最新技術 GPT-4V(GPT-4 Vision)をベタ褒めしたばかりですが、今日は少し厳しいテストをしてみましたので報告させて頂きます。(表題の ChatGPT-4V は、正確には GPT-4V と書くべきですが、分かりやすさ優先とさせて頂きました。)

なお、いずれも 2023年10月頃に評価したものです。将来は、改善される可能性があります。

最初はスゴいと思ったんだけど…

GPT-4V が使えるようになった頃(10月初旬)、GPT-4V が回路図を理解できるかどうか、実験したことがあります。具体的には、以下のような 2つの回路図でテストしました。

- Latches in Digital Logic – GeeksforGeeks(NAND ゲートで実装された SR ラッチ回路)

- How does NE555 timer circuit work | Datasheet | Pinout | ElecCircuit.com(タイマ IC 555 で実装した回路)

それぞれ、ChatGPT による対話を引用してみましょう。

私:

(上の GeeksforGeeks のページの最初の回路図を示して)ディジタル回路図のようなのですが、これはどういう回路ですか?

ChatGPT:

このデジタル回路図は、SRフリップフロップ(Set-Reset Flip-Flop)として知られるものです。フリップフロップは、デジタルロジックの基本的な構成要素の1つであり、1ビットの情報を保存することができます。

このSRフリップフロップは、以下のような動作をします:

-

- S = 1, R = 0 の場合、Q = 1 となり、Q̅ = 0 となります(セット状態)。

- S = 0, R = 1 の場合、Q = 0 となり、Q̅ = 1 となります(リセット状態)。

- S = 0, R = 0 の場合、Q と Q̅ の出力は前回の状態を保持します(メモリ状態)。

- S = 1, R = 1 の場合の動作は未定義とされることが多いです。この状態は通常、避けられるように設計されます。

SRフリップフロップは、情報を一時的に保存するための基本的なデバイスとして、デジタルシステムで広く使用されています。

この回答は実は間違っているのですが、その時は回答に驚いてしまい、間違いに気付きませんでした。

次に、555 タイマのほうです。

私:

(この回路図を示して)これはどうでしょう。アナログ回路みたいですけど。

ChatGPT:

はい、この回路は555タイマーICを使用したアストロブル発振回路の一例です。555タイマーは非常に汎用性のあるICで、様々なアナログおよびデジタルアプリケーションに利用されます。

この特定の回路は、以下のように動作します:

-

- 555タイマーはアストロブルモード(フリーランニングモード)で接続されています。これにより、繰り返しオンとオフを交互にする矩形波を生成します。

- R1、R2、およびC1の値によって、この波形の周波数(または出力のオン/オフのレート)が決定されます。

- この回路では、出力の周波数は約1Hzに設定されており、LED1は約1秒ごとにオンとオフを繰り返します。

この回路は、シンプルなタイマーや警告ライト、点滅信号など、多くのアプリケーションで使用される基本的な点滅回路の例として見ることができます。

私:

R1, R2, C1 の値から発振周波数を計算する式を教えてください。

ChatGPT:

もちろん、555タイマーをアストロブルモードで使用するときの発振周波数は、以下の式を使用して計算できます。

f = 1.44 / ((R1 + 2R2) × C1)

ここで、

-

- は発振周波数(Hz)

- および は抵抗の値(オーム)

- はコンデンサの値(ファラド)

この式を使用すると、与えられたR1、R2、およびC1の値から555タイマーの出力周波数を計算できます。

私:

値を代入して計算してください。

ChatGPT:

了解いたしました。与えられた値を式に代入して計算します。

発振周波数 の計算式は以下です。(略)

この式に値を代入すると、(略)

したがって、回路の発振周波数は約1.03Hzです。

SR ラッチのときと違い、これは合ってそうですね。(アナログ設計の専門家が見たら、ダメだしがあるかも知れませんが。)

私の回路図も見て貰おう!(アナログ回路編)

今日になって、そのときの感動を思い出し、そうだ、私が書いた回路図でも正しく解釈してくれるのだろうか? と考えました。まずは、コピー用紙にラフに手書きの回路図を描いて試してみます。

これは、定電圧レギュレターIC 7805 を使った応用電源回路です。わくわくしながら実験してみます。

私:

これは電子回路図だと思うのですが、この回路図について説明してください。

ChatGPT:

はい、この図は電子回路図の一部と思われます。

回路の中心部にある「7805」という部品は、一般的にはリニア電圧レギュレータとして知られています。特に、7805は5Vの正の固定出力電圧レギュレータとして使用されることが多いです。この部品の目的は、入力電圧を安定した5Vの出力電圧に変換することです。

次に、この図には2つのキャパシタ、C1とC2があります。これらのキャパシタは、通常、電圧レギュレータの入力と出力の両方でノイズを低減するために使用されます。特に、リニアレギュレータの周りには、安定性を高めるためにデカップリングキャパシタが推奨されることが多いです。

そして、Q1というトランジスタが図示されていますが、このトランジスタの具体的な使用目的や動作についての詳細は、この回路図だけでは確定的には分かりません。しかし、Q1は入力側に接続されており、何らかのスイッチングや保護機能を果たしている可能性が考えられます。

総じて、この回路は5Vの電源を供給するためのもので、特に7805レギュレータを中心としたシンプルな設計となっていると思われます。ですが、Q1の具体的な役割や、他の部品との関連については、より詳しい回路の説明や文脈が必要です。

いい線を行っているとも言えますが、期待ほどではないですね。助け船を出してみます。

私:

低電圧レギュレター(補足: 定電圧の誤記)の電流容量を増やすためのものかも知れません。

ChatGPT:

おっしゃる通りで、Q1トランジスタが含まれているという点から、これは「増幅トランジスタ」を使用して7805リニアレギュレータの出力電流容量を増加させるための回路である可能性が高いです。

簡単に説明すると、リニアレギュレータの出力電流はそのままでは限られていますが、外部トランジスタを追加することで、この制限を超える電流を流すことができるようになります。このような設計は、大きな電流を必要とする負荷を駆動する場合や、レギュレータ自体の熱を減少させたい場合などに有効です。

Q1トランジスタは、7805からの出力電流の大部分を取り扱い、7805自体の電流負荷を軽減します。これにより、全体としての出力電流容量が増加します。

この回路設計の注意点として、Q1の選択や、7805のサーマルデザイン、さらには適切なヒートシンクの使用などが重要となります。これにより、回路全体の動作を安定させ、過熱を防ぐことができます。

悪くはないですが、私はもうちょっと突っ込んだ回路の解説を期待していたので、少し拍子抜けしました。

別の回路図も見て貰おう!(SR ラッチ編)

次に、SR ラッチ回路をラフスケッチして GPT-4V に見て貰います。

私:

この電子回路について説明してください。

ChatGPT:

この画像には、2つの電子スイッチまたはトランジスタのようなコンポーネントが描かれています。それぞれのコンポーネントは、入力(IN1、IN2)と出力(OUT1、OUT2)を持っています。

ただし、具体的な部品の種類や機能(例: トランジスタの種類、MOSFETまたはBJTなど)や、具体的な動作(例: スイッチとしての動作、アンプとしての動作など)は、この図だけでは判断することが難しいです。

この図からは、単に2つのスイッチまたはトランジスタの基本的な接続を示しているだけで、詳細な動作や回路の全体的な機能についてはわかりません。もし、この回路の詳しい情報や動作に関する質問があれば、お気軽に教えてください。

うーん、私の絵が下手なのは分かってますけど…。

私:

2つの素子はNANDロジックだと思うのですが。

ChatGPT:

了解しました。おっしゃる通り、この図をNANDゲートとして解釈すると理解が進むかと思います。

NANDゲートは基本的なディジタルロジックゲートの1つで、2つの入力が両方とも「1」(高)の場合にのみ出力が「0」(低)となり、それ以外の場合には出力が「1」(高)となる特性を持っています。

この図の場合、上のゲートは入力がIN1、出力がOUT1、下のゲートは入力がIN2、出力がOUT2となります。

したがって、

-

- IN1とIN2が両方とも「1」の場合: OUT1とOUT2は「0」

- IN1またはIN2が「0」の場合: OUT1またはOUT2は「1」

という動作をすることが期待されます。

この解釈が正しければ、図は2つの独立したNANDゲートを示していることになります。

なんか、ちゃんと分かっていないようです。。。とりあえず、真理値表を書かせてみますか。

私:

真理値表を書けますか?

ChatGPT:

もちろん、NANDゲートの真理値表を書きます。

以下は2つのNANDゲートの真理値表です。各ゲートの入力と出力を示しています。

IN1 | IN2 | OUT1 | OUT2 ----------------------- 0 | 0 | 1 | 1 0 | 1 | 1 | 0 1 | 0 | 0 | 1 1 | 1 | 0 | 0

この真理値表により、

-

- IN1とIN2の両方が「0」の場合、OUT1とOUT2は「1」

- IN1が「0」、IN2が「1」の場合、OUT1は「1」、OUT2は「0」

- IN1が「1」、IN2が「0」の場合、OUT1は「0」、OUT2は「1」

- IN1とIN2の両方が「1」の場合、OUT1とOUT2は「0」

という動作をすることがわかります。

うーん、順序回路だということを理解できていないようです。

私:

この回路はフィードバックがあるので、ステートフルな記憶回路だと思うのですが。

ChatGPT:

申し訳ございません。おっしゃる通りです。お示しいただいた回路にはフィードバックが存在するため、それはステートフルな記憶回路、具体的にはSRラッチ回路の一形態と見ることができます。

SRラッチの真理値表を作成いたします:

S (IN1) | R (IN2) | Q (OUT1) | ~Q (OUT2) --------------------------------------- 0 | 0 | No Change | No Change 0 | 1 | 0 | 1 1 | 0 | 1 | 0 1 | 1 | Invalid | Invalid

-

Sが1、Rが0のとき、Q(OUT1)は1にセットされ、~Q(OUT2)は0にリセットされます。Sが0、Rが1のとき、Q(OUT1)は0にリセットされ、~Q(OUT2)は1にセットされます。SおよびRの両方が0の場合、Qと~Qの状態は変わりません。SおよびRの両方が1の場合は、無効な入力となります。この状態は通常、使用されるべきではありません。

このラッチは、2つの状態を持つことができるため、情報(ビット)を記憶することができます。

うーん、S と R の論理が逆のようです。

私:

逆だと思うのですけど。

ChatGPT:

申し訳ございません。おっしゃる通り、間違いを犯してしまいました。もう一度、SRラッチの真理値表を作成いたします。

正しくは、以下の通りです:

S (IN1) | R (IN2) | Q (OUT1) | ~Q (OUT2) --------------------------------------- 0 | 0 | Invalid | Invalid 0 | 1 | 1 | 0 1 | 0 | 0 | 1 1 | 1 | No Change | No Change

-

Sが1、Rが0のとき、Q(OUT1)は0にリセットされ、~Q(OUT2)は1にセットされます。Sが0、Rが1のとき、Q(OUT1)は1にセットされ、~Q(OUT2)は0にリセットされます。SおよびRの両方が1の場合、Qと~Qの状態は変わりません。SおよびRの両方が0の場合は、無効な入力となります。この状態は通常、使用されるべきではありません。

再度、ご指摘いただきありがとうございます。正確な情報を提供できず、申し訳ございません。

ようやく正しくなりました。

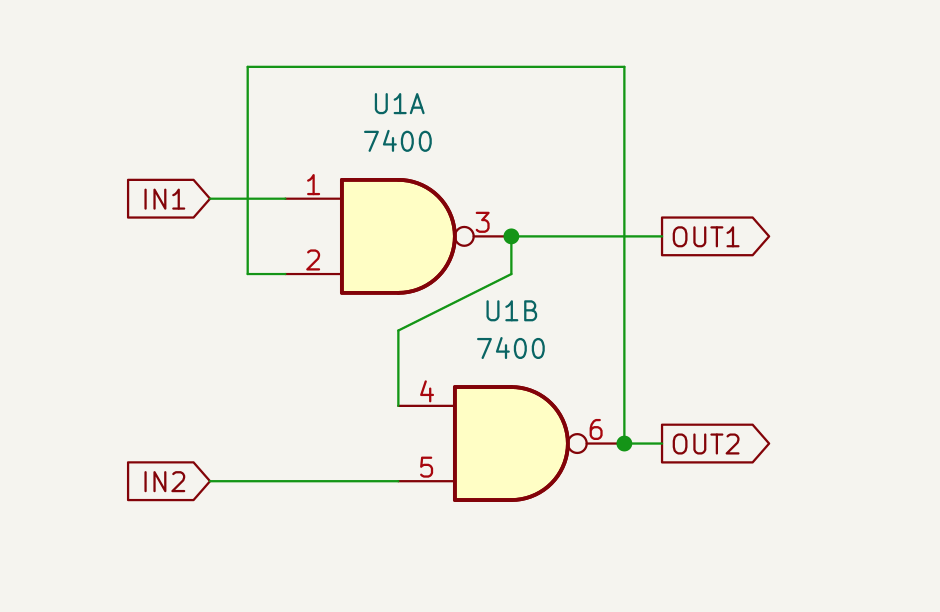

手書きだからいけないのか? KiCad で描いてみた

私の回路が手描きだからいけないのでしょうか。KiCad を引っ張り出して、回路を描いてみました。

ここで、少し意地悪をしてみます。よくあるように配線を中央でクロスさせるのでなく、あまり一般的でない描き方をしてみました。これは、ChatGPT が本当に回路図を読めているかどうかの試験なのです。

私:

この回路について説明してください。

ChatGPT:

この回路は、7400シリーズのTTL ICを使用した基本的な回路の一部を示しています。7400は4つの2入力NANDゲートを内蔵しています。

回路の詳細は以下の通りです:

-

- U1Aは7400の1つ目のNANDゲートを示しています。入力はIN1としてラベル付けされており、このゲートの出力はOUT1に接続されています。

- U1Bは7400の2つ目のNANDゲートを示しています。入力はIN2としてラベル付けされており、このゲートの出力はOUT2に接続されています。

簡単に言えば、この回路は2つの独立したNANDゲートを示しており、それぞれのゲートは異なる入力を受け取り、それに基づいて出力を生成します。NANDゲートは、両方の入力が「1」(または「HIGH」)の場合にのみ「0」(または「LOW」)を出力し、それ以外のすべての入力の組み合わせで「1」を出力します。

この回路は、論理操作や他のデジタル回路とのインタフェースなど、様々なアプリケーションに使用することができます。

どうも、この回路が SR ラッチだと気付いていないようです。

結論

冒頭の GeeksforGeeks のページの回路図では SR ラッチだと理解できているので不思議ですね。私の想像ですが、GPT-4V は、回路図を見て実際に配線を追う能力はないのではないかと思います。ネット上に見られる回路図の「雰囲気」だけを知っていて、与えられたのと似たような画像を探し出し、その回路図の説明を反復しているだけのような気がしてきました。

まとめてみましょう。GPT-4V(GPT-4 Vision)は、

- ネット上でよく見られるような回路図については、アナログ回路もディジタル回路も、それがどのような目的の回路図なのか、概ね理解できる。

- 回路図が掲載されているウェブサイトの説明は、概ね理解できているようだ。

- ただし、論理を正しく解釈できている訳ではないので、回路の論理を正しく理解できているとは限らない。

- 手描きの回路図でも、回路図中の文字は認識できているようだが、記号(NAND ゲートなど)は、印刷物のものほど正確には認識できない。

今後も、GPT Vision の技術改良に注目して参りましょう!