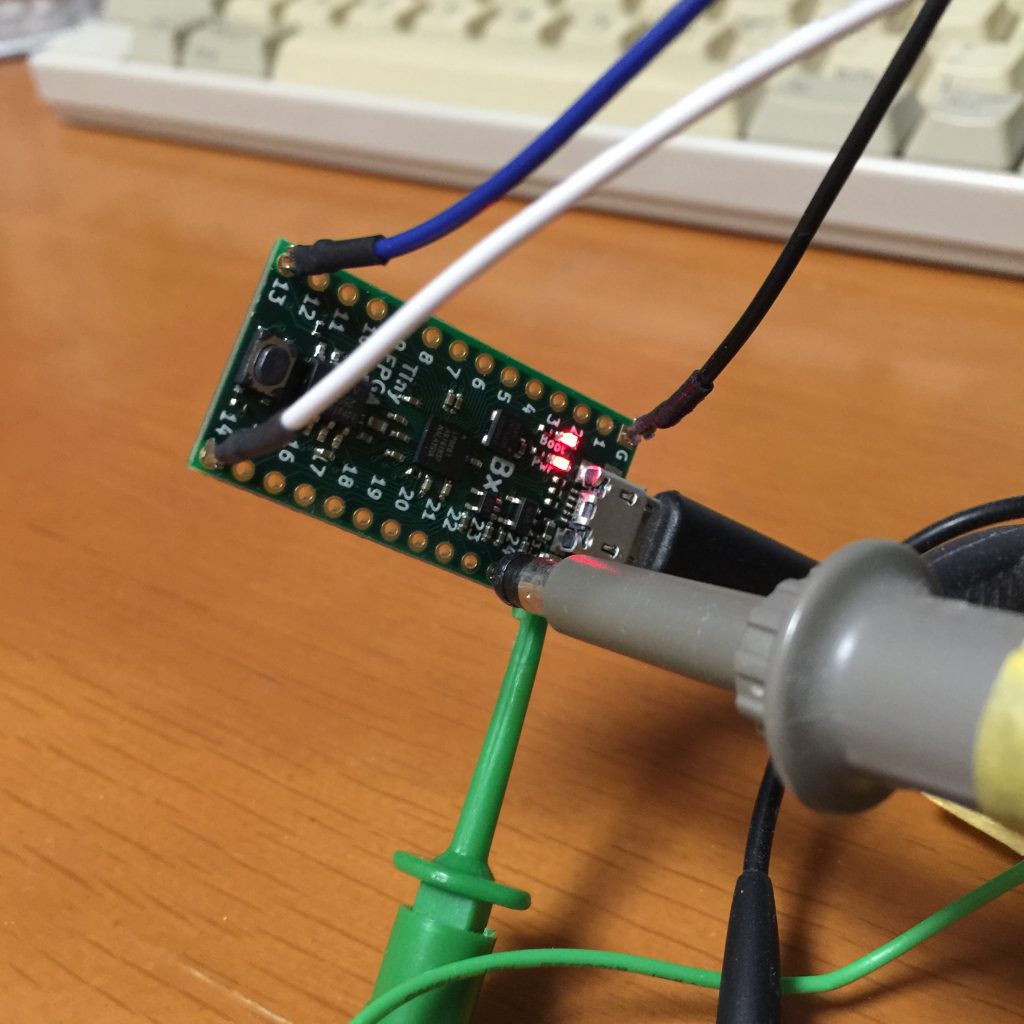

Just ran softcore processor VexRiscv (RISC-V of course) on TinyFPGA-BX without XIP functionality.

相変わらずの SpinalHDL 日和です。 🙂

今日は、RISC-V ソフトコアプロセッサ実装で有名な VexRiscv を、これまた有名な FPGA ボード TinyFPGA-BX で動かしてみました。技術的には難しくないと思うのですが、SpinalHDL を知らないと、ちょっとハードルが高いです。(そのような訳で、いままでずっと SpinalHDL を勉強してきた次第です。)

詳細は以下を御覧ください。

Murax SoC

今回ポーティング(というほどではないですが)したのは、VexRiscv の作者さんが公開している Murax という小さな SoC です。Murax の特徴をまとめると、

- VexRiscv RV32I(M はオプション。今回は無し)

- JTAG デバッグ機能(Eclipse/GDB/OpenOCD 対応)

- オンチップ RAM(8 キロバイト)

- 割込コントローラあり

- 内蔵ペリフェラルのための APB(バス)

- GPIO ピン 32本

- 16ビットタイマ

- UART

です。

以下、結果だけをまとめておきます。

ロジックセルの使用量

以下、nextpnr からの情報です。TinyFPGA-BX が持つ logic cell 7680個のうち、だいたい 1/3 くらいに納まっています。ちょっとした使い方ならば十分ではないでしょうか。

Info: Device utilisation: Info: ICESTORM_LC: 2437/ 7680 31% Info: ICESTORM_RAM: 22/ 32 68% Info: SB_IO: 16/ 256 6% Info: SB_GB: 8/ 8 100% Info: ICESTORM_PLL: 0/ 2 0% Info: SB_WARMBOOT: 0/ 1 0%

タイミング解析

$ icetime -tmd lp8k bin/Murax_iCE40_tinyfpga_bx.asc

Total number of logic levels: 9

Total path delay: 23.27 ns (42.98 MHz)だいたい 42MHz で動作することが分かります。なお、同じ iCE40 FPGA でも、HX タイプを使うともっと高速に動くようです(60MHz くらい)。

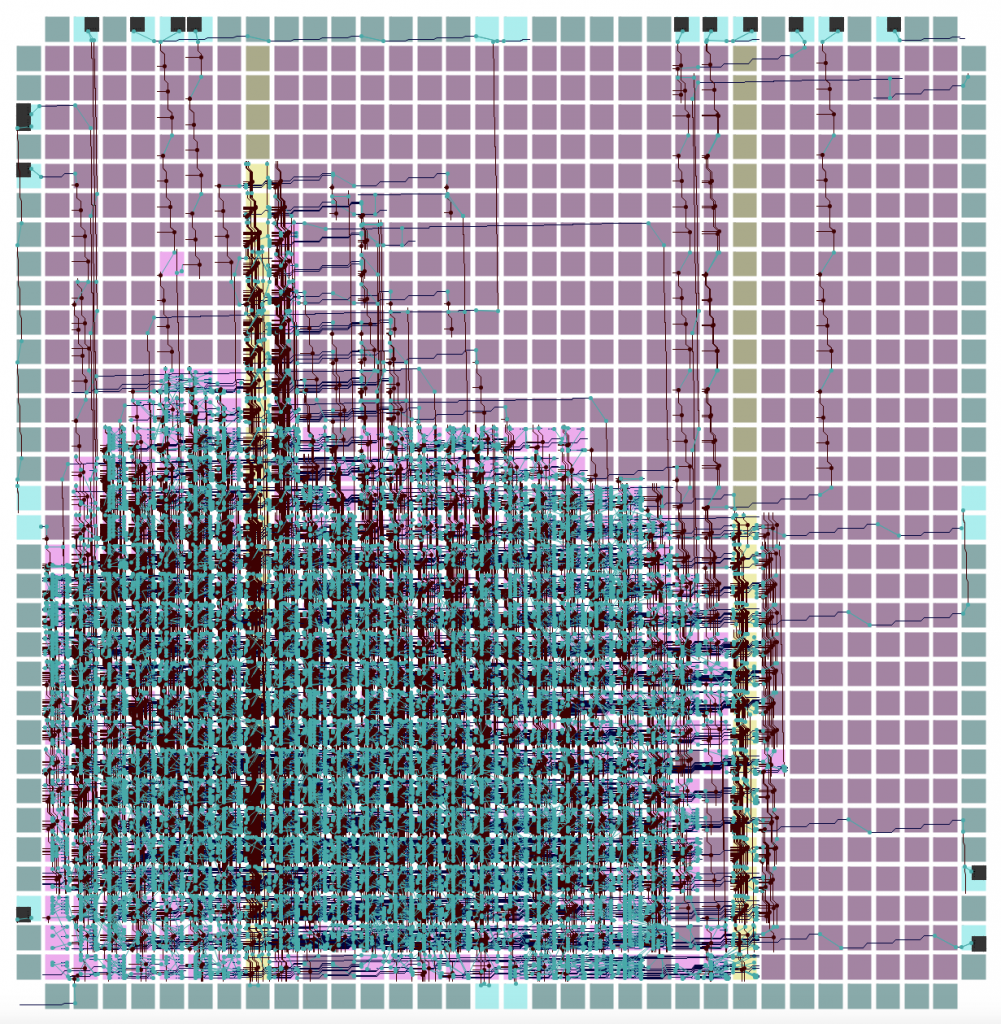

お約束のフロアビュー

今後の宿題

- OpenOCD + JTAG によるデバッグ

- もう少し高度なファームウェアプログラミング

- 乗算器の評価

- 自作ペリフェラル回路の接続

- PLL を載せて 42MHz で動かす

- フラッシュメモリ上での XIP(eXecute-In-Place)にも挑戦してみたい

今日はここまで。