Slowly start learning LiteX and Migen. 以前に、SpinalHDL というハードウェア記述言語や、オープンソース(あまり好きな言葉ではないが)の論理合成ツール Yosys、Place and Route ツール nextpnr を使って、設計した論理回路や RISC-V SoC を Lattice 社の FPGA 上で動かしてました。 SpinalHDL による SoC 設計は面白いのですが、SpinalHDL プロジェクトの進み方は基本… 続きを読む »

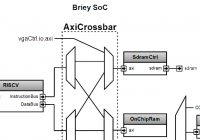

Running VexRiscv SoC with AXI4 crossbar on TinyFPGA BX. 前回まで、VexRiscv プロジェクトで公開されている Murax という SoC で遊んで来ました。Murax は非常に小型の SoC 実装例(デモ)となっていて、小さな論理規模で実装できるのがポイントです。しかしながら、私は今後、この SoC に CPU 以外のバスマスタ(DMA)を追加する実験をしたいと思っており、この Murax が持っているバス Mura… 続きを読む »

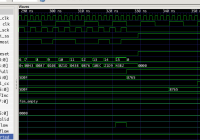

Added SPI Peripheral functionality to Murax (free RISC-V SoC). 以前、TinyFPGA BX 上で動作する VexRiscv SoC Murax に PWM 機能を追加してみましたが、今回はもう少し実用的なペリフェラルとして、SPI ペリフェラルインターフェイスを追加してみました。目的の一つとして、クロックドメインをまたぐ設計を少し勉強してみたい、ということがあります。 SPI ペリフェラル機能の設計自身も、実は私… 続きを読む »

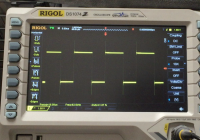

Added a PWM output control to VexRiscv (RISC-V) Murax Soc. 先日、VexRiscv Murax SoC を TinyFPGA-BX で動かす修正を御紹介しましたが、今回は自分で書いた小さな小さなペリフェラル(PWM 出力)を APB3 バス経由で Murax SoC に繋いでみました。 SpinalHDL によるコードは非常にシンプルで明解です。じゃん。 package flogics.vexriscv.pwm imp… 続きを読む »

ファームロジックスでは、組込ソフトウェア技術を中心とした試作や設計サポート、技術トレーニングを提供しています。国内最大手通信機器メーカー 6社の半導体技術サポート(11年間)と、通信機器設計(8年間)の実績を元に事業を行っています。これに加え、IoT(モノのインターネット)、組込機器のセキュリティ対策まで、組込ソフトウェア設計を中心に、お客様の技術導入や御社内トレーニングをお手伝いします。 技術対応やお客様対応でお困りの同業者様からのお問い合わせに関しましては、即日の対応も承… 続きを読む »